Current research activities

Our research focus is on signal processing theory, algorithm development, and digital VLSI circuits and systems for signal and information processing applications requiring highest throughput, lowest latency, and best-in-class results. Our current focus is on low-precision massive multiple-input multiple-output (MIMO) wireless systems, approximate solvers for signal recovery from nonlinear measurements (including phase retrieval problems), analog-to-information (A2I) and analog-to-feature (A2F) converters for low-power classification and inference, as well as real-time image computational imaging. In all these fields, we develop hardware-friendly algorithms, perform a thorough theoretical analysis of the algorithms' performance and complexity, and implement corresponding digital VLSI circuits.

Realizing massive MIMO with approximate algorithms and low-complexity architectures

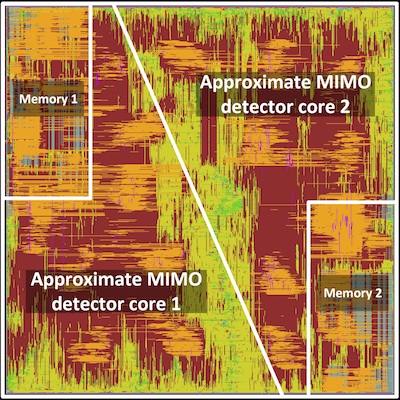

Massive (or large-scale) MIMO is an emerging wireless communication technology that builds upon the idea of having orders of magnitude more antennas at the base station (BS) compared to conventional (small-scale) MIMO systems, while serving tens of users simultaneously and in the same frequency band. This recent technology promises significant improvements in terms of spectral efficiency, link reliability, and coverage. Unfortunately, all these benefits come at the cost of significantly increased computational complexity at the BS for realistic antenna configurations. In particular, data detection in the uplink and precoding in the downlink, as well as impairment compensation, are expected to be among the most critical tasks in terms of complexity and power consumption. Our research aims at developing novel baseband processing algorithms that will enable the benefits of massive MIMO in practical systems at low cost and low power. To this end, we develop novel algorithms, provide corresponding theoretical performance guarantees, and integrate our solutions in ASICs and design FPGA prototypes. The image on the left shows the first data detector ASIC layout for a 3GPP-LTE-based 128-antenna, 8-user massive MIMO system achieving more than 3.8Gb/s.

Selected publications

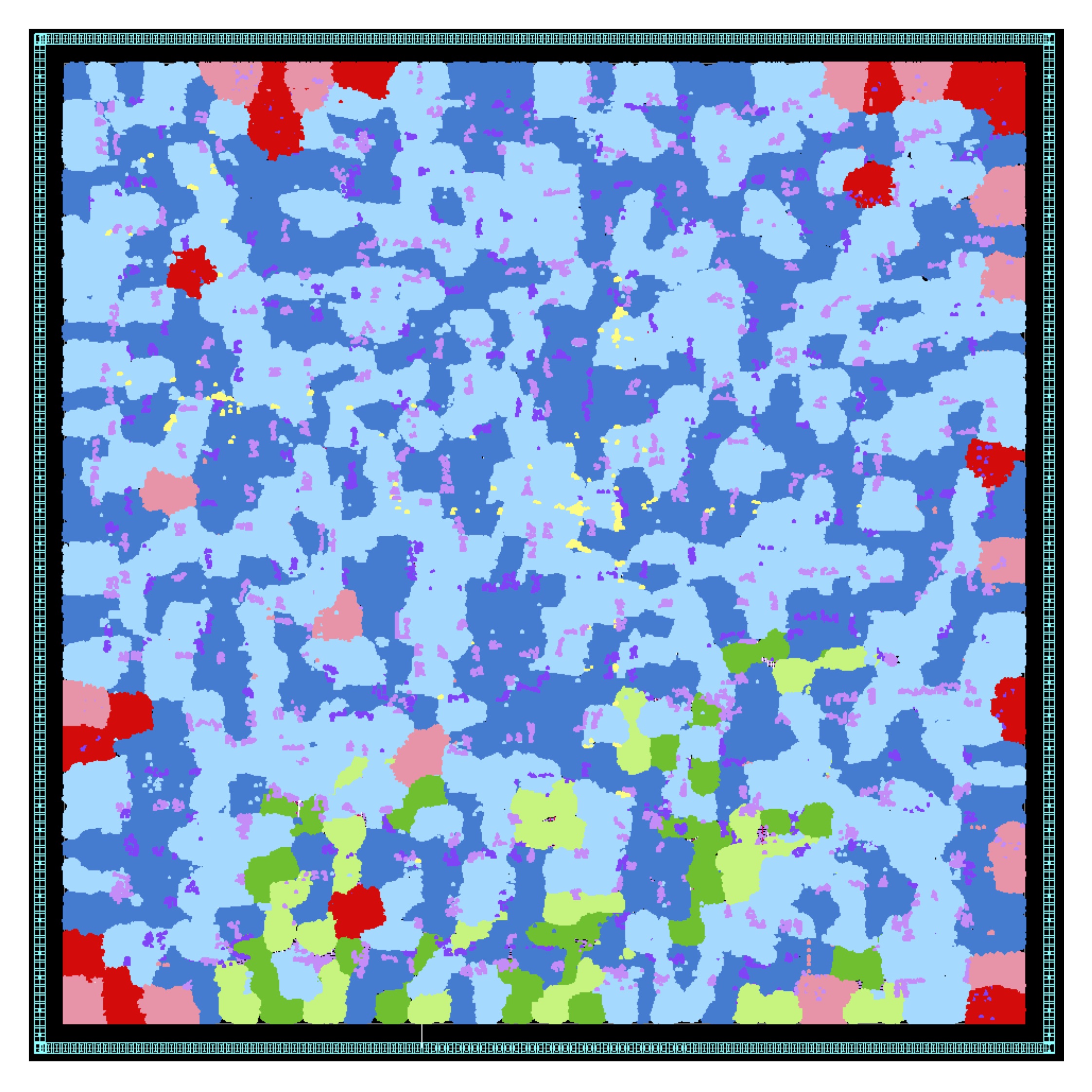

Real-time approximate discrete programming

Discrete programming (DP) deals with optimization problems involving variables that range over a discrete (e.g., binary or integer-valued) solution space. DP is an important tool in a variety of applications including digital communications, operations research, and computer vision. While discrete programs are typically solved offline by sophisticated software using powerful computers, DP has recently emerged as an important tool in applications requiring real-time processing in embedded systems with stringent area, cost, and power constraints. Our research fuses optimization theory, numerical methods, and integrated circuit design to develop fast algorithms and suitable hardware architectures for real-time DP in embedded systems. Our focus is no real-time applications in communication systems, imaging and computer vision, and machine learning. The image on the left shows the first semidefinite relaxation (SDR) solver that has been in VLSI; the solver is called TASER and performs SDR-based data detection in multi-antenna systems with up to 64 users.

Selected publications

Analog-to-information (A2I) and analog-to-feature (A2F) conversion

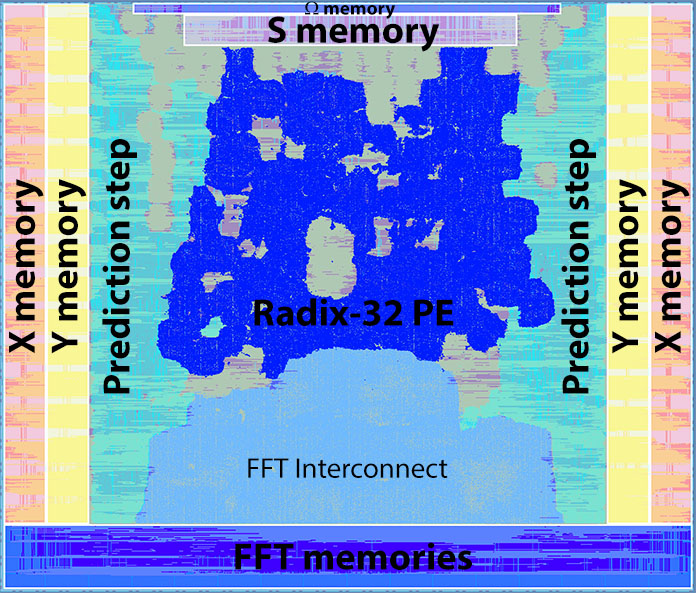

In a large number of communications and signal-processing applications, such as wide-band radio-frequency (RF) spectrum sensing or multi-channel signal acquisition, sensing or sampling signals at the Nyquist rate results in prohibitive data rates and requires power-inefficient and expensive analog-to-digital (ADC) converters. In recent years, advances in compressive sensing and sparse signal processing have shown that signals with low-dimensional structure (e.g., sparsity or low-rank) can be sampled and recovered well-below the Nyquist rate. The main idea is to jointly perform signal acquisition and dimensionality reduction, while preserving the signals' information. Such analog-to-information (A2I) converters enable inexpensive and energy-efficient ways of sampling of analog signals, while sophisticated recovery algorithms extract the information of interest. Most existing A2I solutions perform sampling using dedicated hardware but perform recovery off-line using expensive commodity hardware and computationally complex algorithms. In contrast, we explore novel integrated A2I converter designs that jointly consider sampling and recovery, which enables us to achieve low-latency information recovery at higher bandwidths, as well as novel ways to compensate for system impairments directly within the recovery circuitry. The image on the left shows a 28nm SOI implementation of a novel accelerated sparse signal dequantization (ASSD) engine for A2I-based 6GHz wideband spectrum sensing.

Selected publications

Real-time image computational imaging

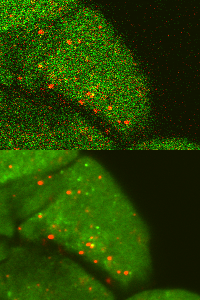

Computational imaging is a fairly new field that fuses optics, imaging sensors, and computation to overcome the limitations of traditional imaging systems (e.g., photo or video cameras, microscopes, etc.). Computational imaging enables, for example, inexpensive light-field, high-speed, or hyperspectral imaging (or a combination thereof), which finds use in a large number of practical applications, ranging from consumer electronics to biology, physics, or defense applications. Unfortunately, computational imaging requires complex algorithms that operate on massive datasets, and is typically deployed in systems with stringent throughput and quality constraints. Existing systems perform the underlying algorithms off-line using expensive and power-inefficient general-purpose processors or graphics processing units (GPUs), which prohibits the use of this technology in portable (battery powered) and real-time imaging systems. To enable computational imaging in real-time systems, we develop new hardware-friendly algorithms that enable real-time processing using field-programmable gate arrays (FPGAs) or application-specific integrated circuits (ASICs). Our main focus is to develop a real-time computational imaging platform that overcomes the limitations of existing off-line prototypes. The image on the left shows a low-light denoising application using fluorescence microscopy; we are currently developing new algorithms and hardware designs that perform this denoising task in real-time on inexpensive FPGA platforms.

Selected publications

Sponsors

The support of the following grants, funding agencies, and companies is gratefully acknowledged.

Collaborators

In alphabetical order.